# **Image Compression Using Lifting Scheme**

# Remya.V<sup>1</sup>, Pavithra.S<sup>2</sup>, Swathi.Y<sup>3</sup>, Geetha.B<sup>4</sup>

Department of Electronics and Communication Engineering, Sri Sairam Engineering College, West Tambaram, India.

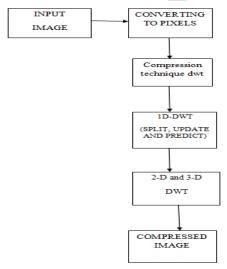

Abstract— To transmit an image the bandwidth should be less. This can be achieved by compression. Moreover to reduce the storage capacity, the image should be compressed. Many applications in medical field involves various types of diagnostic imaging. There are many methods by which image compression can be done. Wavelet transform method is the most prominent method because of its multiresolution and scaling property. A new method known as lifting wavelet is proposed in this paper. In comparison with various other techniques the lifting scheme allows reconstruction by its structure. The prominent feature of this concept is that it is simple and the compression speed is fast and also it can be quickly applications into FPGA chip. It requires fewer operations and provides inplace computation of the wavelet coefficients.

A method which implements 3-D lifting wavelet by FPGA is proposed in this paper. To implement highthroughput processing without any on-chip memory/first in first out access, an efficient pipeline structure is used. The proposed VLSI architecture is more efficient than the previous proposed architectures in terms of memory hardware regularity and simplicity and access, throughput.

Keywords— Discrete Wavelet Transform, Very-Large-Scale Integration (VLSI), High-Speed, Lifting Scheme.

## I. INTRODUCTION

Because of the recent advancements in medical imaging and telecommunication systems, the compression techniques require efficient speed, resolution and real-time memory optimization with maximum hardware utilization. For medical imaging systems because of perfect reconstruction requirement, the 3D Discrete Wavelet Transform (DWT) are more frequently used. DWT can decompose the signals into different sub bands with both time and frequency information and facilitate to arrive at high compression ratio. DWT architecture, in general, reduces the memory requirements and increases the speed of communication by breaking up the image into the blocks.

A methodology for implementing lifting based DWT has been proposed because of lifting based DWT has many advantages over convolution based one. The lifting structure largely reduces the number of multiplication and accumulation where filter bank architectures can take advantage of many low power constant multiplication algorithms. FPGA is used in general in these systems due to low cost and high computing speed with reprogrammable property.

#### II. EXISTING SYSTEM

In the existing method, the floating point MAC based 1D/2D-DWT, where the high/low pass filter outputs are found by MAC. In the existing method, the Convolution based floating point 2D-discrete wavelet transform architecture is proposed, which is designed with floating point multiply accumulate circuit (MAC).

#### III. PROPOSED SYSTEM

This system proposes the 3D- DWT using lifting scheme. The lifting scheme entirely relies on the spatial domain, has many advantages compared to filter bank structure, such as lower area, power consumption and computational complexity. The lifting scheme can be easily implemented by hardware due to its significantly reduced computations. Lifting has other advantages, such as "in-place" computation of the DWT, integer-to-integer wavelet transforms which are useful for lossless coding.

#### IV. RELATED WORK

Wavelet transform has gained widespread acceptance in image compression research in particular. In addition, several VLSI architectures have been proposed for computing the 3D-DWT. They are mainly based on convolution scheme and lifting scheme. The lifting scheme can reduce the computational complexity by exploiting the similarities between high and low pass filters and it usually requires fewer multipliers and adders than the convolution scheme.

This architecture, uses many large multiplexers for storing intermediate results. The 2-D architecture employs a folding technique. An efficient VLSI implementation of Distributed Architecture for DWT in order to minimize area requirement, but they have a computation time which is proportional to input data. The 2-D DWT architecture which composes of simple processing units and computes one stage of DWT at a

The VLSI architecture for DWT is classified into two categories, they are

- Convolution based.

- Lifting based.

# A. Convolution Technique

The convolution technique as depicted in fig1 can be done in 2 steps, they are row process and column process. Here, the input signal sample values are represented as a N × N matrix. During the row process, each row of the input signal matrix is 1D transformed and the results are stored in  $N \times N2$ buffer.

After completing all the N rows of input signal matrix, transpose matrix of the buffer is taken for column process. In column process, each row of transposed buffer matrix is 1D transformed and results are the required 2Dtransformed values.

Fig 1. Convolution Algorithm

#### B. LIFTING TECHNIQUE

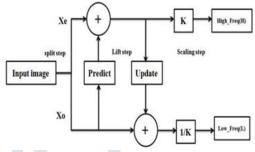

The main feature of the lifting scheme is that all constructions are derived in the spatial domain. The steps to be followed in lifting scheme is as shown in Fig2. Lifting scheme is a simple and an efficient algorithm to calculate wavelet transforms as a sequence of lifting steps. Constructing wavelets using lifting scheme comprises three steps:

- 1. Split step: The original signal, input image X (n), is split into odd and even samples.

- 2. Lifting step: This step is executed as N sub steps depending on the type of the filter, where the odd and even samples are filtered by the prediction and update filters, p(z) and u(z).

- 3. Normalization or Scaling step: After N lifting steps, scaling coefficients K and 1/K are applied respectively to the odd and even samples in order to obtain the low pass sub band i.e. significance coefficient YL (i) and the highpass sub band i.e. detailed coefficient YH.

Fig 2. Lifting Algorithm

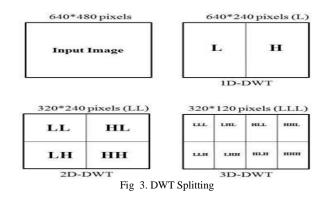

Fig 3. depicts the DWT splitting formats. In ID-DWT the entire 640\*480 pixels are splitted into two 640\*240 pixels i.e., low (L) and high (H). In 2D-DWT again the Low level pixels are reduced to two 320\*240 pixels (LL and HL). Whereas in 3D-DWT, the each matrix of pixels are again splitted into 320\*120 pixels

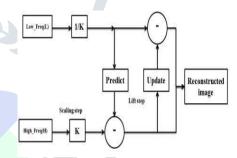

Fig 4 and 5 depicts the steps to be followed in compression by forward lifting and decompression by backward splitting i.e, the reverse of forward splitting

Fig 4. Forward Lifting Scheme

Fig 5. Bakward Lifting Scheme

The proposed work is specialized for the DWT 5/3 wavelet in lifting scheme implementation. "X" be the input image, which has predefined pixels.

Let, X = [X(1), X(2) ... X(2n)] be an array of length 2n

work begins with the "poly-phase This decomposition," splitting X into two sub-bands, each of length N. The original signal i.e. input image pixels are split into even and odd pixels in split step of the design.

$$Xo = [X(1), X(3), X(5)... X(2n-1)]$$

$$Xe = [X (2), X (4), X (6) ... X (2n)]$$

There are four stages in the lifting scheme architecture which is summarized by the equations as follows:

$$P1(n) = Xo(n) + a (Xe(n) + Xe(n+1))$$

$$U1(n) = Xe(n) + b (P1(n) + Xe(n+1))$$

dc(n) = k \* P1(n)

sc(n) = 1/k \* U1(n)P1(n) and U1(n) are scaled by the constant K and K-1 respectively, for normalizing their magnitude. Filter coefficients are described in table 1. The inverse transform is done by performing the lifting steps in the reverseorder and with a, b and k negated.

#### V. RESULT AND SIMULATION

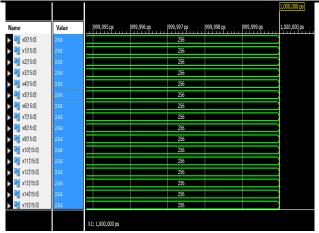

The input of DWT block in 4x4 matrix is shown in fig 5.1 which consists of pixels in binary form.

Fig 5.1. Input of DWT block

## A. DWT Convolution Technique

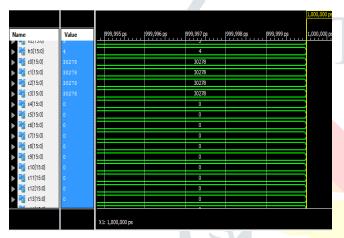

The DWT convolution output is shown in fig 5.2 which shows the pixels in the binary form of the 4x4 matrix. Here the first row of matrix has been filled and the others were filled by spatial domains which indicates that the image has been compressed.

Fig 5.2. Output of DWT Convolution

# B. DWT Lifting Technique

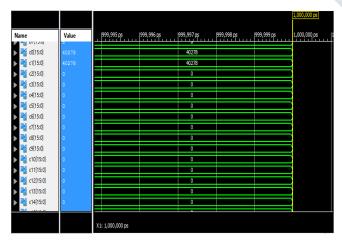

The DWT lifting output is shown in fig 5.3 which shows the pixels in the binary form of the 4x4 matrix. Here only the first two elements of the matrix has been filled and others were spatial domains, this indicates that the image compression has been done more efficiently than convolution technique.

Fig 5.3. DWT lifting output

# C. Comparison of parameters

Table 1 compares the parameters of existing convolution technique and proposed Lifting Scheme. From the table it is clear that the proposed lifting scheme requires less space and computation speed is also increased.

TABLE I. Comparison of parameters

| SYSTEM      | AREA        | DELAY     |

|-------------|-------------|-----------|

| CONVOLUTION | 26754 LUT's | 78.937 ns |

| LIFTING     | 15378 LUT's | 72.607 ns |

#### VI CONCLUSION

The proposed architecture saves embedded memories, decreases computing time, consumes low power, and decreases control complexity. This hardware is designed to be used as part of a complete high performance and low power JPEG2000 encoder system for digital cinema applications. It is also possible to provide multilevel decomposition for 3D-DWT. Also, delay in the design would be optimized. In future this architecture could also extend to multi level DWT.

#### References

- ChengyiXiong, JinwenTian, and Jian Liu, "Efficient Architectures for Two-Dimensional Discrete Wavelet Transform Using Lifting Scheme", IEEE Transactions on Image Processing, 2007, 16 (3), pp. 607-614.

- Chih-Hsien Hsia, Jen-Shiun Chiang, Member, and Jing-Ming Guo, "Memory-Efficient Hardware Architecture of 2-D Dual-Mode Lifting-Based Discrete Wavelet Transform", IEEE Transactions on Circuits and Systems for Video Technology, 2013, 23 (4), pp. 671-683.

- [3] Chu Yu and Sao-Jie Chen, "VLSI Implementation of 2-D Discrete Wavelet Transform for Real-time Video Signal Processing", IEEE Transactions on Consumer Electronics, 1997, 43 (4), pp. 1270-1279.

- [4] Francescomaria Marino, "Efficient High-Speed/Low-Power Pipelined Architecture for the Direct 2-D Discrete Wavelet Transform", IEEE Transactions on Circuits and Systems - II: Analog and Digital Signal Processing, 2000, 47 (12), pp. 1476-1491.

- [5] Guangming S hi, Weifeng Liu, Li Zhang, and Fu Lii, "An Efficient Folded Architecture for Lifting-Based Discrete Wavelet Transform", IEEE Transactions on Circuits and Systems-II: Express Briefs, 200956 (4), pp. 290-294.

- Liu Hong-jin, Shao Yang, He Xing, Zhang Tie-jun, Wang Dong-hui and Hou Chao-huan, "A Novel VLSI Architecture for 2-D Discrete Wavelet Transform", IEEE International Conference on ASIC, Oct. 2007, pp.40-43.

- Mohamed AsanBasiri M and Noor MahammadSk, "An efficient Hardware Based Higher Radix Floating Point MAC Design", ACM Transactions on Design Automation of Electronic Systems (TODAES),2014, 20 (1), pp. 15:1-1.

- Po-Cheng Wu and Liang-Gee Chen, "An Efficient Architecture for Two-Dimensional Discrete Wavelet Transform", IEEE Transactions on Circuits and Systems for Video Technology, 2001, 11 (4), 536-

- [9] Tinku Acharya and Chaitali Chakrabarti, "A Survey on Lifting-based Discrete Wavelet Transform Architectures", Journal of VLSI Signal Processing, 2005, 42, pp. 321-339.

- XinTian, Lin Wu, Yi-Hua Tan, and Jin-Wen Tian, "Efficient Multi-Input/Multi-Output VLSI Architecture for Two-Dimensional Lifting-Based Discrete Wavelet Transform", IEEE Transactions on Computers, 2011, 60 (8), pp. 1207-1211K. Elissa, "Title of paper if known," unpublished.